# **Clocks and Triggers**

### Saulius Gražulis

#### Vilnius. 2020

Vilnius University, Faculty of Mathematics and Informatics Institute of Informatics

Attribution-ShareAlike 4.0 International license

Clocks and Triggers

3 1 4

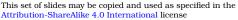

2's complement:  $2^N - b$

э

2's complement:  $2^N - b$

$$egin{array}{ccccccccc} & 1 & 0 & 0 & 0 & 0 \ & b_3 & b_2 & b_1 & b_0 \end{array}$$

$C_3$   $C_2$   $C_1$   $C_0$   $\leftarrow$  2's complement (complementary code)

$$2^{N} - \mathbf{b} = (2^{N} - 1) - \mathbf{b} + 1$$

2's complement:  $2^N - b$

$$2^{N} - \mathbf{b} = (2^{N} - 1) - \mathbf{b} + 1$$

$$1\,0000_{2} = 1111_{2} + 1$$

2's complement:  $2^N - b$  $2^{N} - b = (2^{N} - 1) - b + 1$  $1\,0000_2 = 1111_2 + 1$  $\overline{b_3}$   $\overline{b_2}$   $\overline{b_1}$   $\overline{b_0}$   $\leftarrow$  1's complement (inverse code) + $C_3$   $C_2$   $C_1$   $C_0$   $\leftarrow$  2's complement

□ > < E > < E > E - のへの

# 2's complement example

$$10_2 - 11_2 = ???$$

$10_2 - 11_2 = 0010_2 + 1101_2 = 1111_2 = -1_2$

・ 何 ト ・ ヨ ト ・ ヨ ト ・ ヨ

| Dec. | 2's Compl. | Dec.    | 2's Compl. |  |

|------|------------|---------|------------|--|

| 7    | 0111       | -1 1111 |            |  |

| 6    | 0110       | -2      | 1110       |  |

| 5    | 0101       | -3 110  |            |  |

| 4    | 0100       | -4      | 1100       |  |

| 3    | 0011       | -5      | 1011       |  |

| 2    | 0010       | -6      | 1010       |  |

| 1    | 0001       | -7      | 1001       |  |

| 0    | 0000       | -8      | 1000       |  |

· < A → < 3

| Dec. | 2's Compl. | Dec. | 2's Compl.   |

|------|------------|------|--------------|

| 7    | 0111       | -1   | <b>1</b> 111 |

| 6    | 0110       | -2   | <b>1</b> 110 |

| 5    | 0101       | -3   | <b>1</b> 101 |

| 4    | 0100       | -4   | <b>1</b> 100 |

| 3    | 0011       | -5   | <b>1</b> 011 |

| 2    | 0010       | -6   | <b>1</b> 010 |

| 1    | 0001       | -7   | <b>1</b> 001 |

| 0    | 0000       | -8   | <b>1</b> 000 |

The most significant bit (MSB) of a negative number is  $\mathbf{1}$

| Dec.     | 2's Compl. | Dec.       | 2's Compl. |

|----------|------------|------------|------------|

| 7        | 0111       | -1         | 1111       |

| 6        | 0110       | 10 -2 1110 |            |

| 5        | 0101       | -3         | 1101       |

| 4        | 0100       | -4         | 1100       |

| 3        | 0011       | -5         | 1011       |

| <b>2</b> | 0010       | -6         | 1010       |

| 1        | 0001       | -7         | 1001       |

| 0        | 0000       | -8         | 1000       |

The most significant bit (MSB) of a negative number is **1** The smallest representable negative number has absolute value *larger* than the larger representable positive.

| Dec. | 2's Compl. | Dec. | 2's Compl. |

|------|------------|------|------------|

| 7    | 0111       | -1   | 1111       |

| 6    | 0110       | -2   | 1110       |

| 5    | 0101       | -3   | 1101       |

| 4    | 0100       | -4   | 1100       |

| 3    | 0011       | -5   | 1011       |

| 2    | 0010       | -6   | 1010       |

| 1    | 0001       | -7   | 1001       |

| 0    | 0000       | -8   | 1000       |

$$1011_{2} = 1000_{2} + 0011_{2} = -2^{3} + 11_{2}$$

$$= 1^{-2^{3}} 2^{2} 2^{1} 2^{0}$$

$$= -2^{3} + 2^{1} + 2^{0} = -8_{10} + 2_{10} + 1_{10}$$

$$= -5_{10}$$

Saulius Gražulis

Vilnius, 2020 4 / 29

3

イロト イポト イモト イモト

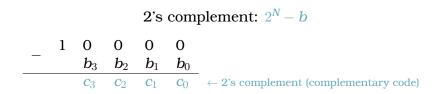

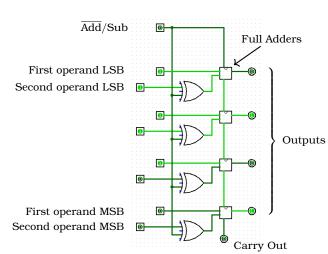

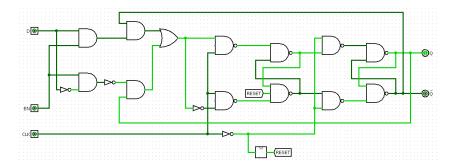

### Adder/Subtractor ALU

$$7_{10} + 3_{10} = 0111_2 + 0011_2 = 1010_2 = 10_{10}$$

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 5 / 29

### Adder/Subtractor ALU

$7_{10} - 3_{10} = 0111_2 - 0011_2 = 0111_2 + 1101_2 = 1\ 0100_2 = 4_{10}$

# Other representations of negative numbers

Signed magnitude:

$$6_{10} = 0110_2; \quad -6_{10} = 1110_2$$

Complement arithmetic:

$$a + (-b) = a + \underbrace{((2^N - 1) - b)}_{\text{one's complement}} + 1 - 2^N$$

Excess *K* (biased) representation:

$$egin{array}{lll} K=&2^{N-1} & ext{(as a rule, but other values are possible)} \ b\leftrightarrow & K+b &=2^{N-1}+b \ -b\leftrightarrow K+(-b) = 2^{N-1}+(-b) \end{array}$$

Saulius Gražulis

Vilnius, 2020 6 / 29

# Other representations of negative numbers

| Number | Unsigned | 2's Compl. | 1's Compl. | Sign-Magn. | Exess <sup>1</sup> K |

|--------|----------|------------|------------|------------|----------------------|

| 7      | 111      | -          | -          | -          | -                    |

| 6      | 110      | -          | -          | -          | -                    |

| 5      | 101      | -          | -          | -          | -                    |

| 4      | 100      | -          | -          | -          | -                    |

| 3      | 011      | 011        | 011        | 011        | 111                  |

| 2      | 010      | 010        | 010        | 010        | 110                  |

| 1      | 001      | 001        | 001        | 001        | 101                  |

| 0      | 000      | 000        | 000        | 000        | 100                  |

| -0     | -        | -          | 111        | 100        | -                    |

| -1     | -        | 111        | 110        | 101        | 011                  |

| -2     | -        | 110        | 101        | 110        | 010                  |

| -3     | -        | 101        | 100        | 111        | 001                  |

| -4     | -        | 100        | -          | -          | 000                  |

See also:

Murdocca et al. 1999, chapt. 2; Walker 1996, "Minus Zero"

${}^{1}K = 4 = 2^{N-1}$ . N = 3

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 7 / 29

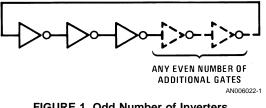

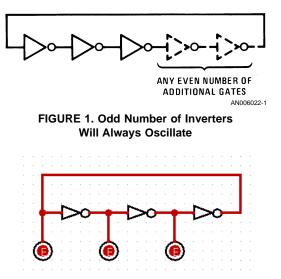

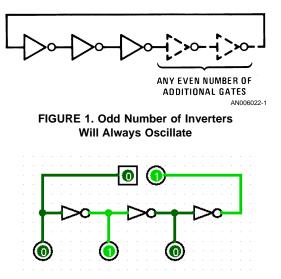

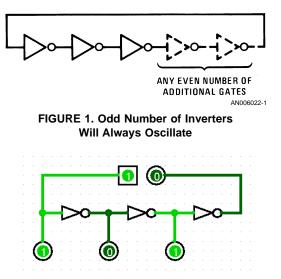

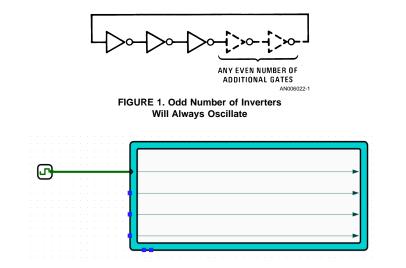

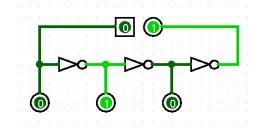

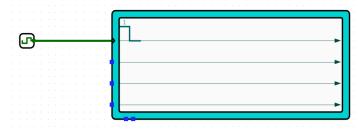

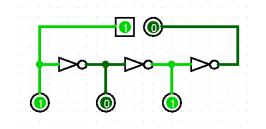

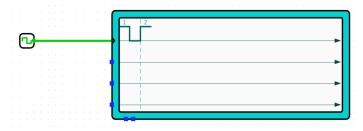

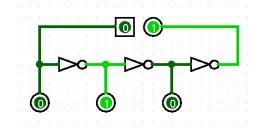

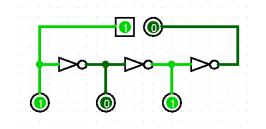

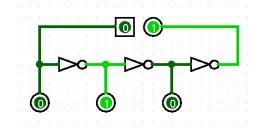

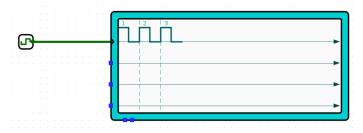

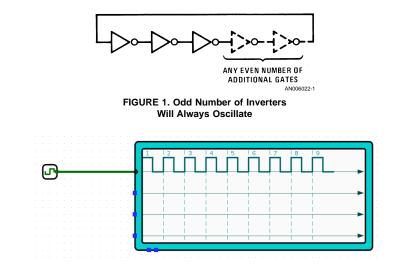

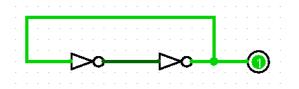

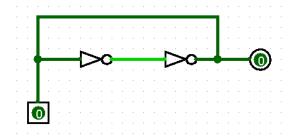

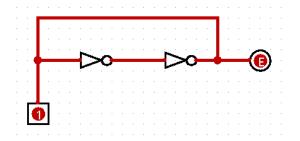

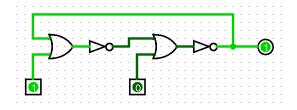

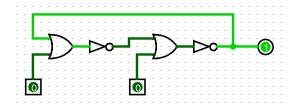

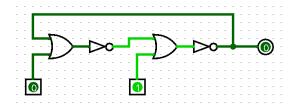

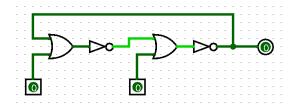

### **CMOS** Oscillators

Fairchild Semiconductor Application Note 118 October 1974

ADDITIONAL GATES

#### FIGURE 1. Odd Number of Inverters Will Always Oscillate

#### (Fairchild Semiconductor 1974)

イロト イポト イモト イモト

Saulius Gražulis

Clocks and Triggers

### **CMOS Oscillators**

Fairchild Semiconductor Application Note 118 October 1974

"It then becomes obvious that a "1" chases itself around the ring and the network oscillates." :)

#### FIGURE 1. Odd Number of Inverters Will Always Oscillate

(Fairchild Semiconductor 1974)

< □ > < 同 > < 回 > < 回 > < 回 >

∃ ► < ∃</p>

Saulius Gražulis

Vilnius, 2020 10 / 29

Saulius Gražulis

Vilnius, 2020 10 / 29

æ

Saulius Gražulis

Vilnius, 2020 10 / 29

æ

Saulius Gražulis

Vilnius, 2020 10 / 29

æ

Saulius Gražulis

Vilnius, 2020 10 / 29

æ

Saulius Gražulis

Vilnius, 2020 10 / 29

æ

イロト イポト イモト イモト

Saulius Gražulis

Vilnius, 2020 10 / 29

æ

Saulius Gražulis

Vilnius, 2020 10 / 29

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 11/29

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 11/29

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 11

11/29

Setting state

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 12 / 29

3 1 4

Setting state

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 12 / 29

∃ ► 4

Setting state

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 12 / 29

3 1 4

Setting state

Saulius Gražulis

Clocks and Triggers

э Vilnius, 2020 12/29

∃ ► 4

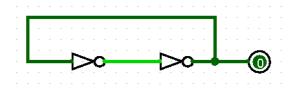

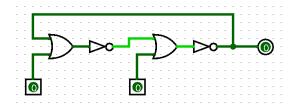

### Even number of inverters

Setting state

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 12 / 29

3 1 4

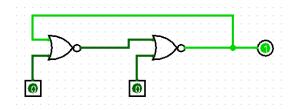

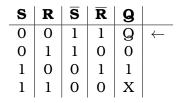

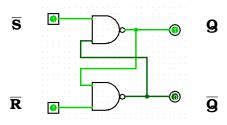

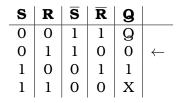

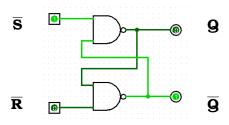

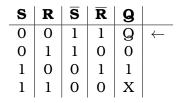

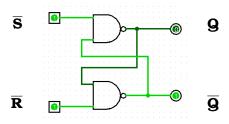

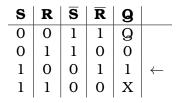

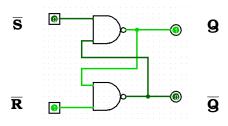

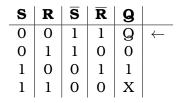

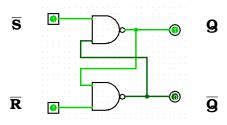

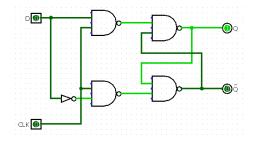

# RS trigger from NOR gates

イロト イポト イヨト イヨ

# RS trigger from NOR gates

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 13 / 29

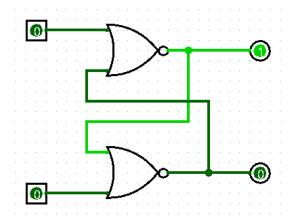

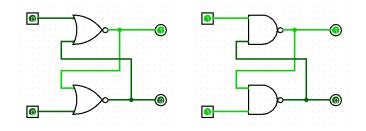

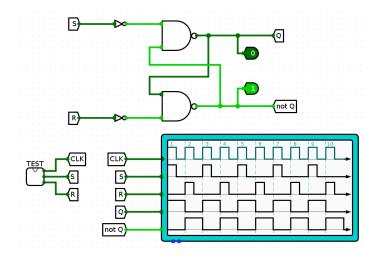

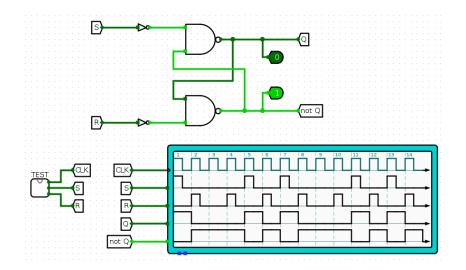

# RS trigger from NOR and NAND gates

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 14

æ

イロト イポト イモト イモト

14/29

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 1

イロト イポト イヨト イヨト

15/29

æ

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 15 / 29

æ

イロト イロト イヨト イヨト

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 1

イロト イポト イヨト イヨト

æ

15/29

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020

イロト イポト イヨト イヨト

15/29

æ

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 1

イロト イポト イヨト イヨト

15/29

æ

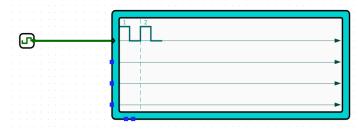

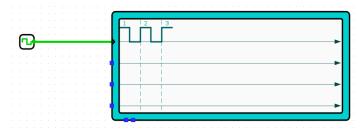

# RS Trigger time traces

æ

イロト イヨト イヨト イヨト

# RS Trigger time traces

æ

・ロト ・ 日 ト ・ ヨ ト ・ ヨ ト

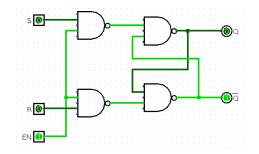

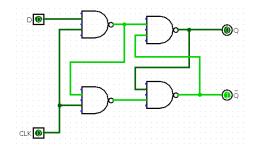

# Gated RS Trigger

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 18

イロト イヨト イヨト イヨト

18/29

æ

#### D Latch

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 19 / 29

æ

◆□▶ ◆圖▶ ◆臣▶ ◆臣▶

#### D Latch

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 19 / 29

æ

◆□▶ ◆圖▶ ◆臣▶ ◆臣▶

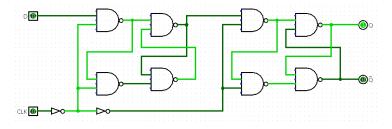

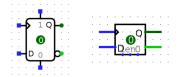

# Edge-triggered D-flip-flop

| Saulius Gražulis | Saul | lius | Gra | ıžu | lis |

|------------------|------|------|-----|-----|-----|

|------------------|------|------|-----|-----|-----|

Vilnius, 2020 20 / 29

2

イロト イポト イヨト イヨト

# Edge-triggered D-flip-flop

Saulius Gražulis

Vilnius, 2020 20 / 29

æ

イロト イポト イモト イモト

### Operation of a D-flip-flop

Saulius Gražulis

Vilnius, 2020 21/29

æ

・ロト ・ 日 ト ・ ヨ ト ・ ヨ ト

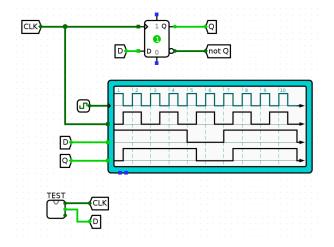

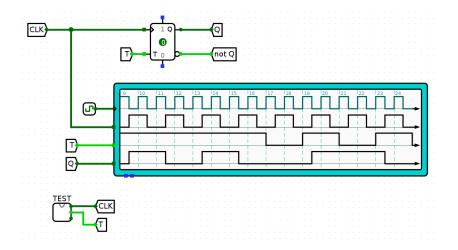

# T flip-flop

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 22 / 29

æ

イロト イロト イヨト イヨト

# Operation of a T-flip-flop

Saulius Gražulis

Vilnius, 2020 23 / 29

イロト イ理ト イヨト イヨト

æ

▲□▶ ▲圖▶ ▲臣▶ ▲臣▶

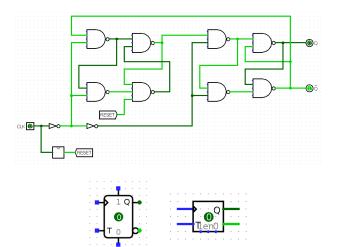

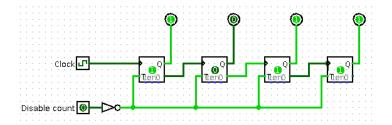

#### Counters

Saulius Gražulis

Clocks and Triggers

Vilnius, 2020 <u>2</u>

æ

・ロト ・ 日 ト ・ ヨ ト ・ ヨ ト

25 / 29

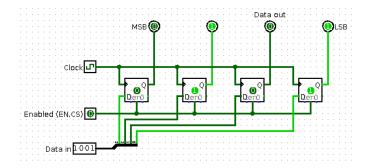

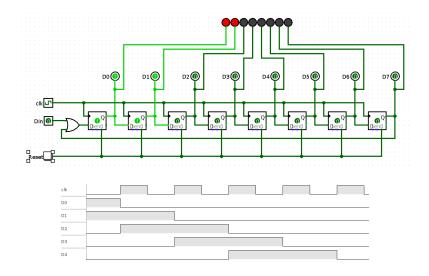

# Shift registers

æ

イロト イポト イヨト イヨ

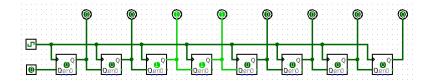

#### Circular shift registers

Saulius Gražulis

Vilnius, 2020 27 / 29

æ

イロト イポト イヨト イヨ

- Negative integers are represented in 2's complement in modern computers, but other methods exist and are also used.

- Modern computers are synchronous they use clock generators to drive their computations

- Feedback is essential to build clocks and memory cells

- From the fundamental RS trigger, gated latches and edge triggered flip-flops (D-, T-flip-flops) are built.

- From D- and T-flip-flops we can further build essential computer components: registers and counters.

- Fairchild Semiconductor (1974). CMOS oscillators. Tech. rep. ON Semiconductor. URL: https://www.onsemi.com/pub/Collateral/AN-118.pdf.pdf.

- Murdocca, Miles J. et al. (1999). Principles of Computer Architecture. Prentice Hall.

- Walker, John (Aug. 19, 1996). *Minus zero*. eng. URL: http://www.fourmilab.ch/documents/univac/minuszero.html.

過き くまき くまき