#### Intel x86 CPU architecture

#### Saulius Gražulis

Vilnius, 2020

Vilnius University, Faculty of Mathematics and Informatics Institute of Informatics

This set of slides may be copied and used as specified in the Attribution-ShareAlike 4.0 International license

# What is a processor architecture?

#### Architecture visible to programmer:

- The CPU registers visible to programmer

- Memory addressing

- Data formats

- Processor instruction set

- Input-output

- Interrupt processing

#### A bit of history

- 1974 8080 8-bit; Addr: 16 bit (64K)

- 1978 8086, 8088 16-bit; Addr: 20 bit (1MB)

- 1982 Intel<sup>®</sup> 286 16-bit (protected memory);

Addr: 24 bit (16MB)

- 1985 Intel386<sup>TM</sup> 32-bit; Addr: 32 bit (4GB);

- 1989 Intel486<sup>TM</sup> 32-bit (+FPU, more instr.);

Addr: 32 bit (4GB);

- 1993 Intel<sup>®</sup> Pentium<sup>®</sup> 32-bit (faster, more instr.); Addr: 32 bit (4GB);

- 1995-1999 The P6 Family of Processors 32-bit;

Addr: 32 bit (4GB);

- 1999 AMD Opteron 64-bit; Addr: up to 64 bit

- 2001-2007 The Intel<sup>®</sup> Xeon<sup>®</sup> 64-bit, Addr: up to 64 bit.

(Intel 2020)

(Intel 1990)

#### **Notational Conventions**

- #GP(0) An instruction exception—in this example, a general-protection exception with error code of 0.

- 1011b A binary value—in this example, a 4-bit value.

- DEAD\_BEEFh A hexadecimal value. Underscore characters may be inserted to improve readability.

- 128 Decimal number, unless the context indicates otherwise.

- 7:4 A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first. Commas may be inserted to indicate gaps.

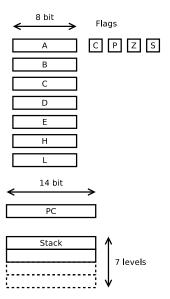

# Registers (x86) – history: 8008

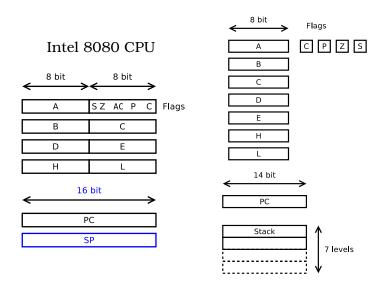

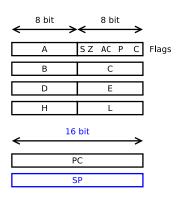

## Registers (x86) – history: 8080

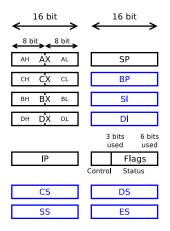

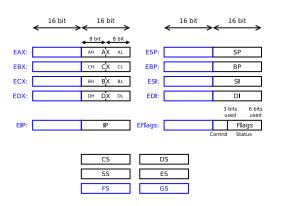

## Registers (x86)

#### Intel 8086 CPU

(Intel 1979)

https://www.youtube.com/watch?v=7xwjjolDnwg

## Registers (80386)

#### Intel 80386 CPU

https://www.youtube.com/watch?v=7xwjjolDnwg

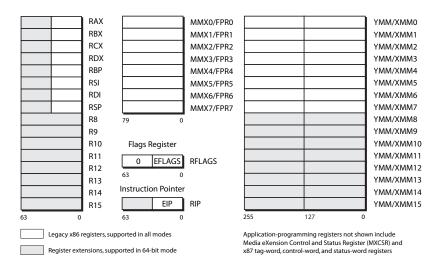

## Registers (x86\_64)

(AMD 2017), here and further: reproduced with AMD permission

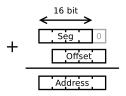

# Segmented addressing

Segment address is shifted by 4 bits and added to the offset:

## Memory layout

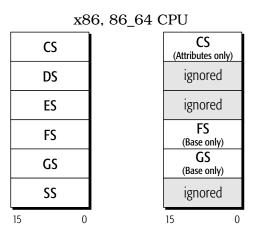

## Segment Registers

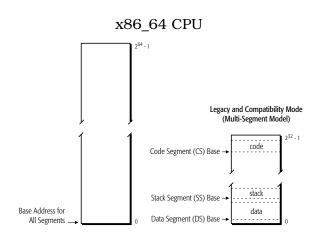

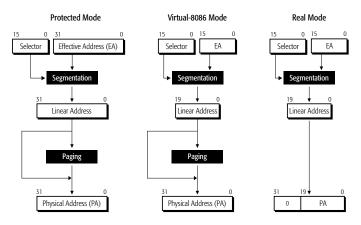

## Legacy mode memory management

x86, 86\_64 CPU

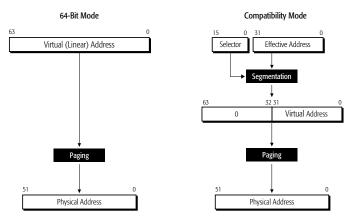

# Long-mode memory management

x86, 86\_64 CPU

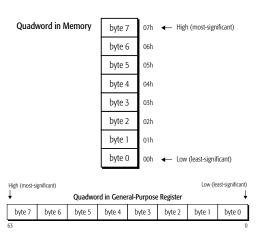

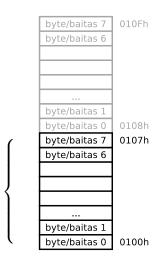

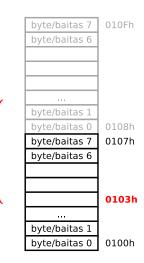

# Byte order

## Instructions in memory

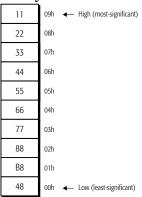

#### Example of 10-Byte Instruction in Memory

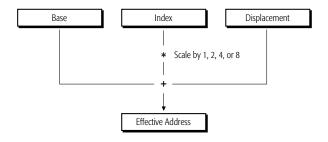

#### Complex address calculation (protected mode)

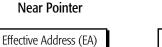

## Near and far pointers

Far Pointer

Selector Effective Address (EA)

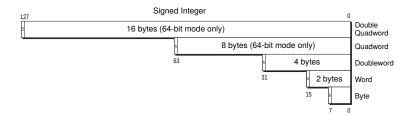

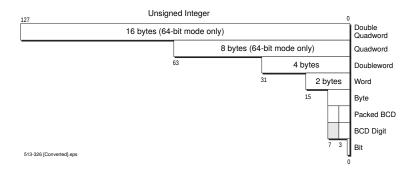

# Basic data types

## Basic data types

## Memory alignment

## Memory alignment

# Take-home message

- The x86 processor architecture stayed compatible (on the binary code level!) with the original 8086/8088 for more than 40 years (!)

- Aligned memory access is as a rule faster for all CPU architectures and required for some of them

- The x86\_64 architecture features flat memory model, 16 64-bit general purpose registers, 16 vector registers and 8 floating point registers

#### References

- AMD (Dec. 2017). AMD64 Architecture Programmer's Manual, Volume 1: Application Programming, revision 3.22. AMD. URL:

- https://www.amd.com/system/files/TechDocs/24592.pdf.

- Intel (Oct. 1979). Intel 8086 Family User's Manual. Intel Corporation. URL: https://edge.edx.org/c4x/BITSPilani/EEE231/asset/8086\_family\_Users\_Manual\_1\_.pdf.

- (1990). 8086 16-bit HMOS microprocessor. Intel Corporation. URL: https://www.manualslib.com/download/77669/Intel-8086.html.

- (May 2020). Intel® 64 and IA-32 Architectures Software Developer's Manual. Vol. 1-5. Intel Corporation. URL: https:

- //software.intel.com/content/www/us/en/develop/download/intel-64-and-ia-32-architectures-sdm-combined-volumes-1-2a-2b-2c-2d-3a-3b-3c-3d-and-4.html.